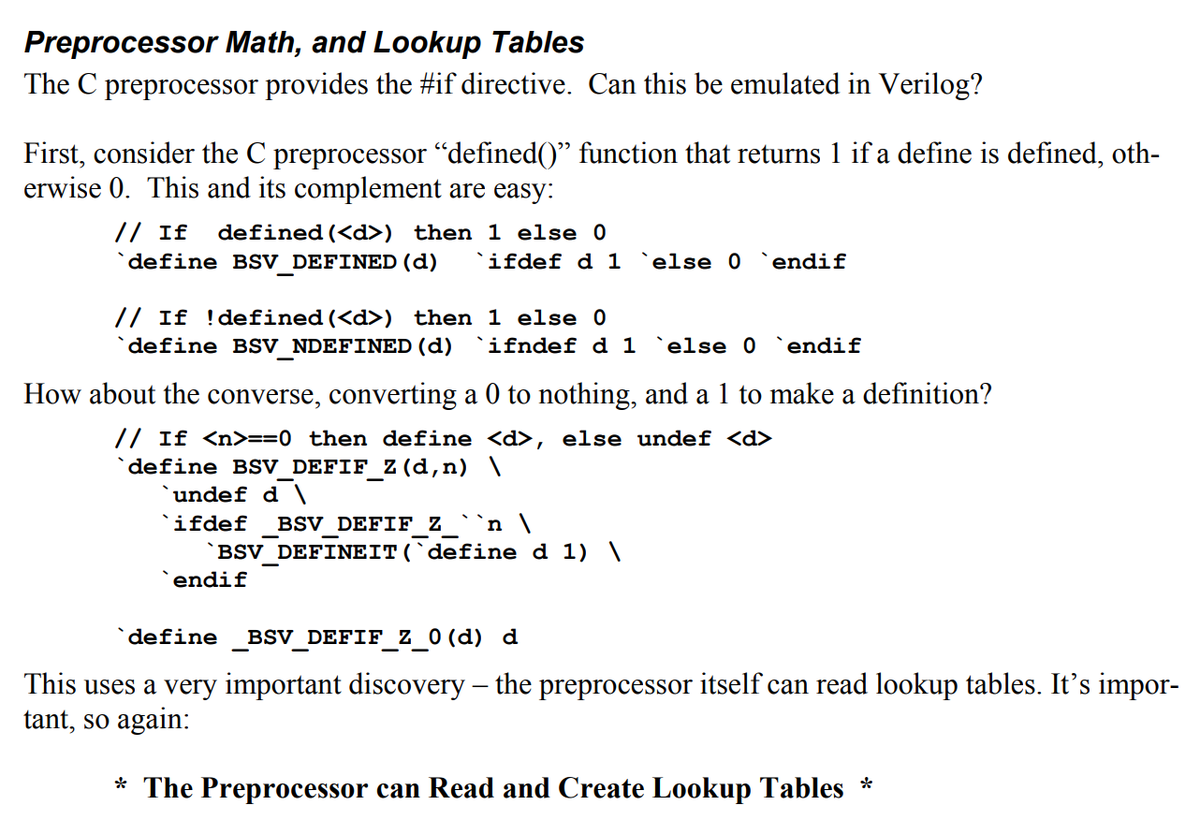

`endif end endmodule a_module ()Jul 11, 13Using the GUI to define the 'ifdef doesn't help I have verilog like 'ifdef PARAM_1 INST_ASIC_MEM_1 'elsif INST_ASIC_MEM_2 'else INST_FPGA_MEM In this case I want the 'else to be executed I have set the PARAM_1 &Mar 26, 151,2 Activity points 1,3 I've been trying to run a simulation for the following sample code Requirement Based on parameters generate a define which will be used further in the design Observation I can make this work if the defines are not used in the port definitions and only in the Behavioral code Code Verilog expand

Ppt Verilog For Computer Design Powerpoint Presentation Free Download Id

Verilog ifdef define

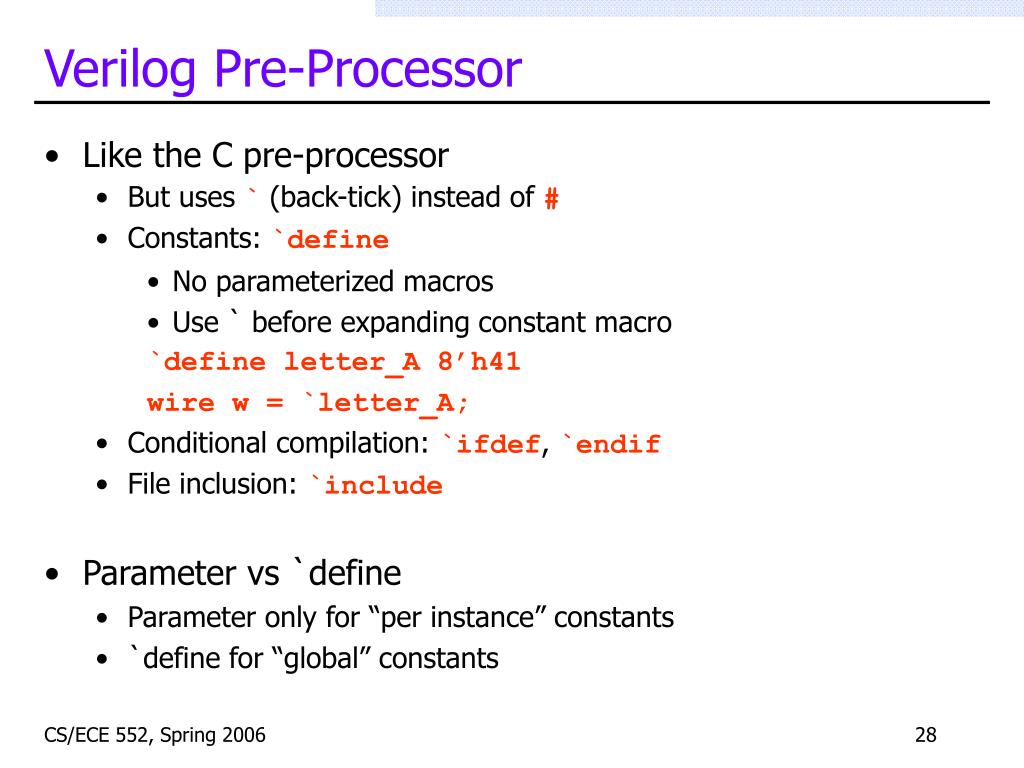

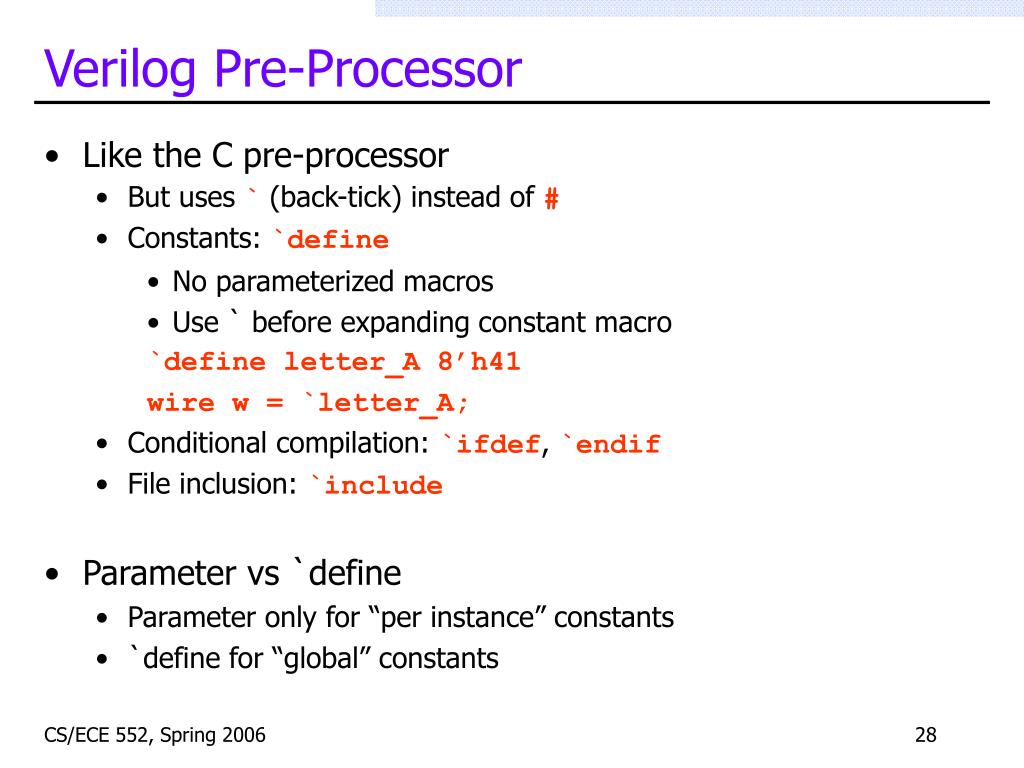

Verilog ifdef define-Verilog preprocessing provides the following features • define option to the analyze command • dc_shell variables • The'ifdef, 'else, and 'endif directives • The DC Macro • Extended capabilities for the'define directive Define Option to the analyze Command An option to the analyzecommand, define(or d, abbreviated),Within the SymbiYosys script section Multiple files may be given on the sames line, or various files may be read in subsequent lines read formal will also define the FORMAL macro, which can be used to separate a section having formal properties from the rest of the logic within the core

Ppt Verilog For Computer Design Powerpoint Presentation Free Download Id

`ifdef, `ifndef, `elsif, `else and `endif conditionally compiles Verilog code, depending on whether or not a specified macro is defined Any code that is not compiled must still be valid Verilog code `include includes the contents of another Verilog source fileSystemVerilog 05 `` `" `\`" SystemVerilog 09 `define MACRO(arg=default) `undefineallThe `define compiler directive is used to perform global macro substitution and remain active for all files read/compiled after the macro definition It will available until another macro definition changes the value or until the macro is undefined using the `undef compiler directive `define WIDTH 8 to avoid redefincation `ifdef can be used, `ifdef WIDTH // do nothing (better to use

In VerilogXL you can define compiler directives by using the define command line switch For example verilog defineFOOBAR f simvc;Jun 24, 21A compiler directive in one file can therefore control compilation behavior in multiple description files VerilogAMS generally support the following compiler directives `default_discipline `default_transition `define `else `endif `ifdef `ifndef `include `resetall `timescale `undef This is only a partial list the directives that areI have 2 macros in verilog used them as below `define TB_4 `define TB_8 `ifdef TB_4 `define tab_4 `define tab_8 `else `ifdef TB_8 `define tab_1

'endif `include <Verilog file>Conditional compilation can be achieved with Verilog `ifdef and `ifndef keywords These keywords can appear anywhere in the design and can be nested one inside the other The keyword `ifdef simply tells the compiler to include the piece of code until the next `else or `endif if the given macro called FLAG is defined using a `define directive`ifdef FLASH_IS_1MB `define FLASH_TEA //19s max for 1MB erase cycle `elsif FLASH_IS_512KB `define FLASH_TEA //12s max for 512KB erase cycle `elsif FLASH_IS_256KB `define FLASH_TEA //6s max for 256KB erase cycle `elsif FLASH_IS_128KB `define FLASH_TEA //4s max for 128KB erase cycle `endif

Fatal Error No Top Model Has Been Defined Troubleshooting Help Tinyfpga

Verilog Posted Hardware Description Language Vhdl

Overriding `define s in Verilog Srini, It depends on the simulator you are using;In this Verilog tutorial, we demonstrate usage of Verilog `define text macros, and `ifdef compiler directiveComplete example from the Verilog tutorial httpAug 25, 10The Verilog preprocessor was first standardized in Verilog , and has been improved with each subsequent standard Reviewing some of the changes Verilog 1995 `define MACRO `ifdef `else `endif `include Verilog 01 `define MACRO(arg) `ifndef `elsif `undef `line SystemVerilog 05 `` `" `\`" SystemVerilog 09

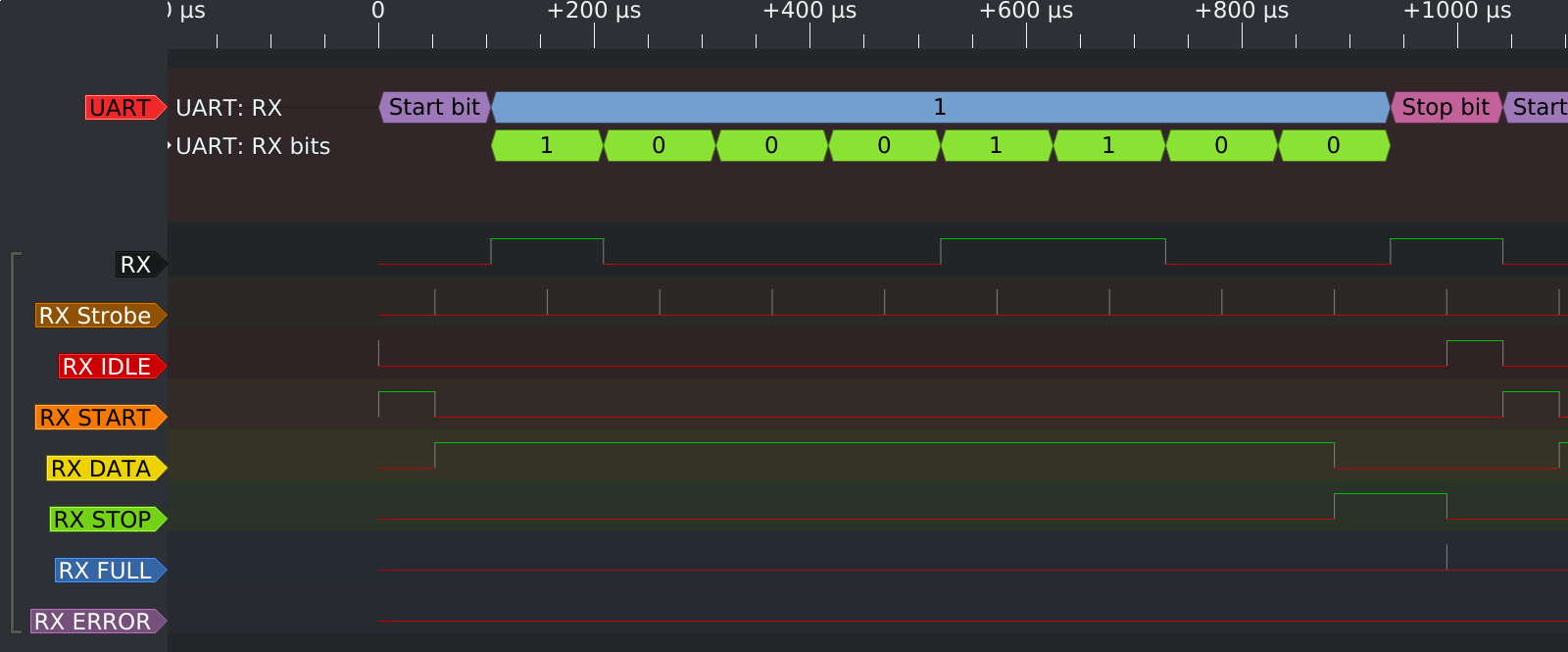

Implementing A Uart In Verilog And Migen Whitequark S Lab Notebook

Whitequark Verilog Doesn T Provide An Equivalent Of C S If Because This Could Result In Bugs Or Something Also Verilog Allows Macro Expansions To Define New Macros

A

0 件のコメント:

コメントを投稿